Interrupt

ARM Interrupt Structure

https://www.geeksforgeeks.org/arm-interrupt-structure/

GIC

https://wiki.osdev.org/Generic_Interrupt_Controller_versions_3_and_4

Interrupt Types

- Difference between SGI PPI SPI: https://stackoverflow.com/questions/27709349/what-is-the-difference-between-ppi-spi-and-sgi-interrupts

- SGI: Software Generated Interrupt

- PPI: Private Peripheral Interrupt

- SPI: Shared Peripheral Interrupt

Interrupt Trigger Types

Link to original

Edge Triggered

Level Sensitive

https://developer.arm.com/documentation/198123/0302/Arm-GIC-fundamentals

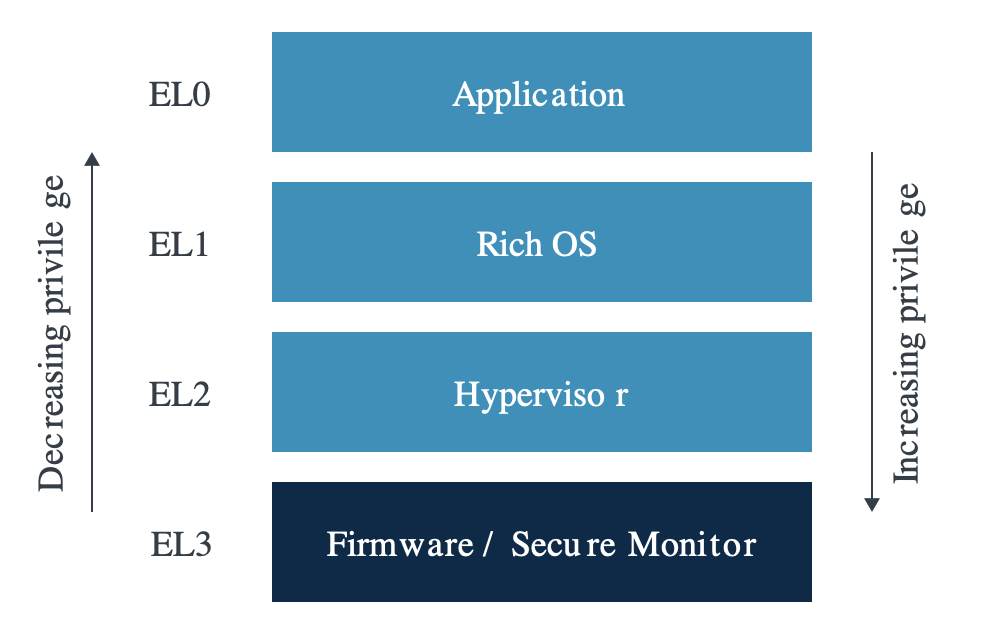

Exception Levels

Exception Levels

Exception Levels

- EL3

- Highest privilege level is typically used for so called

Secure Monitor- EL3 firmware typically implements the Power State Coordination Interface (PSCI) for the lower ELs to use

- EL3 firmware typically involved into trusted boot

- EL2

- Targets the virtualization use-case

- EL at which hypervisors normally use for virtualization purposes.

- EL1

- Privileged parts of the OS kernels use

- EL0

- Most unprivileged level

- Runs most unprivileged codes (userspace application, userspace drivers, etc).

Reference

Link to original

- https://developer.arm.com/documentation/102412/0103/Privilege-and-Exception-levels/Exception-levels

- https://krinkinmu.github.io/2021/01/04/aarch64-exception-levels.html

- https://medium.com/@om.nara/aarch64-exception-levels-60d3a74280e6

Exception Handling

https://developer.arm.com/documentation/dui0471/m/handling-processor-exceptions/exception-handling-process https://developer.arm.com/documentation/100933/0100/Exception-handling https://developer.arm.com/documentation/den0024/a/AArch64-Exception-Handling/Interrupt-handling

Exception Vector

Exception Vector Table

AArch64 Exception Vector Table

ARMv7 Exception Vector Table

Offset Vector Mode 0x00 Reset Supervisor 0x04 Undefined Instruction Undefined 0x08 Supervisor Call Supervisor 0x0C Prefetch Abort Abort 0x10 Data Abort Abort 0x14 Not Used NA 0x18 IRQ Interrupt IRQ 0x1C FIQ Interrupt FIQ ARMv8 Exception Vector Table

Link to original

Address Exception Type Description VBAR_ELn +0x000 Synchronous Current EL with SP0 +0x080 IRQ/vIRQ ^ +0x100 FIQ/vFIQ ^ +0x180 SError/vSError ^ +0x200 Synchronous Current EL with SPx +0x280 IRQ/vIRQ ^ +0x300 FIQ/vFIQ ^ +0x380 SError/vSError ^ +0x400 Synchronous Lower EL using AArch64 +0x480 IRQ/vIRQ ^ +0x500 FIQ/vFIQ ^ +0x580 SError/vSError ^ +0x600 Synchronous Lower EL using AArch32 +0x680 IRQ/vIRQ ^ +0x700 FIQ/vFIQ ^ +0x780 SError/vSError ^