ARM Interrupt Structure

- ARM 아키텍처의 경우 x86아키텍처와는 다르게 Interrupt를 Exception의 일종으로 받아들인다.

- 즉, IDT, IVT가 아닌, Exception Vector Table이 있고, Interrupt 타입인 Exception이 들어오면 어떤 Interrupt인지 그때 확인한 후에 적절한 handler를 실행시켜주어야 한다.

index

Interrupt

ARM Interrupt Structure

https://www.geeksforgeeks.org/arm-interrupt-structure/

GIC

https://wiki.osdev.org/Generic_Interrupt_Controller_versions_3_and_4

Interrupt Types

- Difference between SGI PPI SPI: https://stackoverflow.com/questions/27709349/what-is-the-difference-between-ppi-spi-and-sgi-interrupts

- SGI: Software Generated Interrupt

- PPI: Private Peripheral Interrupt

- SPI: Shared Peripheral Interrupt

Interrupt Trigger Types

Link to original

Edge Triggered

Level Sensitive

https://developer.arm.com/documentation/198123/0302/Arm-GIC-fundamentals

Exception Levels

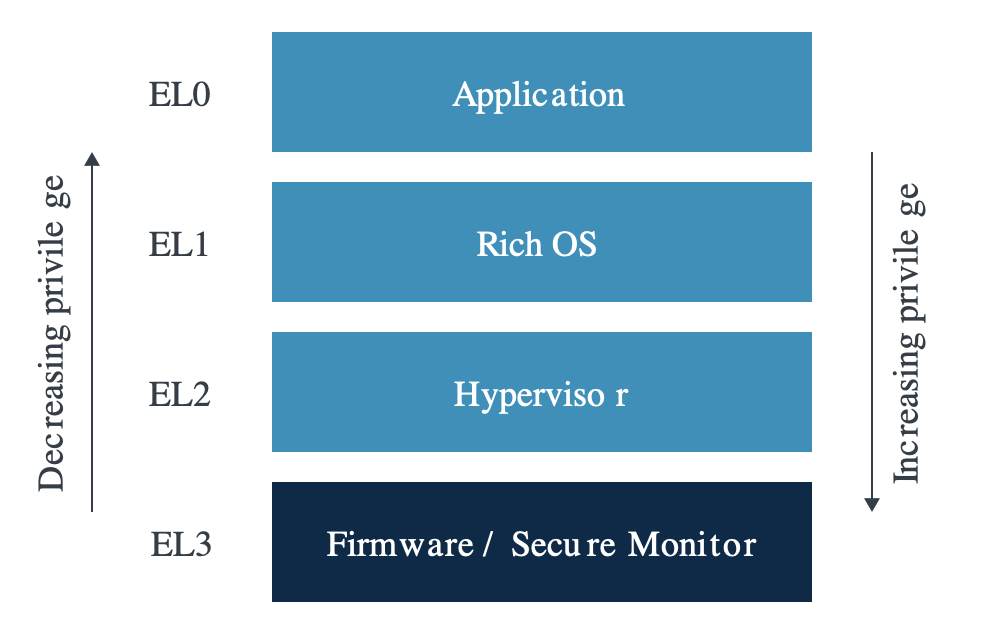

Exception Levels

Exception Levels

- EL3

- Highest privilege level is typically used for so called

Secure Monitor- EL3 firmware typically implements the Power State Coordination Interface (PSCI) for the lower ELs to use

- EL3 firmware typically involved into trusted boot

- EL2

- Targets the virtualization use-case

- EL at which hypervisors normally use for virtualization purposes.

- EL1

- Privileged parts of the OS kernels use

- EL0

- Most unprivileged level

- Runs most unprivileged codes (userspace application, userspace drivers, etc).

Reference

Link to original

- https://developer.arm.com/documentation/102412/0103/Privilege-and-Exception-levels/Exception-levels

- https://krinkinmu.github.io/2021/01/04/aarch64-exception-levels.html

- https://medium.com/@om.nara/aarch64-exception-levels-60d3a74280e6

Exception Handling

https://developer.arm.com/documentation/dui0471/m/handling-processor-exceptions/exception-handling-process https://developer.arm.com/documentation/100933/0100/Exception-handling https://developer.arm.com/documentation/den0024/a/AArch64-Exception-Handling/Interrupt-handling

Exception Vector

Exception Vector Table

AArch64 Exception Vector Table

ARMv7 Exception Vector Table

Offset Vector Mode 0x00 Reset Supervisor 0x04 Undefined Instruction Undefined 0x08 Supervisor Call Supervisor 0x0C Prefetch Abort Abort 0x10 Data Abort Abort 0x14 Not Used NA 0x18 IRQ Interrupt IRQ 0x1C FIQ Interrupt FIQ ARMv8 Exception Vector Table

Link to original

Address Exception Type Description VBAR_ELn +0x000 Synchronous Current EL with SP0 +0x080 IRQ/vIRQ ^ +0x100 FIQ/vFIQ ^ +0x180 SError/vSError ^ +0x200 Synchronous Current EL with SPx +0x280 IRQ/vIRQ ^ +0x300 FIQ/vFIQ ^ +0x380 SError/vSError ^ +0x400 Synchronous Lower EL using AArch64 +0x480 IRQ/vIRQ ^ +0x500 FIQ/vFIQ ^ +0x580 SError/vSError ^ +0x600 Synchronous Lower EL using AArch32 +0x680 IRQ/vIRQ ^ +0x700 FIQ/vFIQ ^ +0x780 SError/vSError ^ Reference

Link to original

- https://velog.io/@coral2cola/ARM-Interrupts-1

- https://velog.io/@coral2cola/ARM-Interrupts-2

- https://grasslab.github.io/osdi/en/labs/lab3.html

Enable & Disable Interrupt

- Enable interrupt:

asm!("msr DAIFClr, #0xf", options(nomem, nostack));MSR DAIFSet, <Xt>: DAIF |= Xt (OR).. 1인 자릿수의 bit 1로 (마스킹하는거)MSR DAIFClr, <Xt>: DAIF &= ~Xt (NAND).. 1인 자릿수의 bit 0으로 (마스킹 안하는거)

- Disable interrupt:

asm!("msr DAIFClr, #0xf", options(nomem, nostack));

DAIF

DAIF: Interrupt Mask Bits

Allows access to the interrupt mask bits. https://developer.arm.com/documentation/ddi0601/2023-12/AArch64-Registers/DAIF—Interrupt-Mask-Bits

D

bit[9]Debug Whether to mask Watchpoint, Breakpoint, Software Step exceptions targeted at the current Exception Level When the target Exception level of debug exception is higher than the current Exception level, the exception will not be masked by D Defaults to 1 on warm reset

D Meaning 0 not masked 1 masked A

bit[8]SError(SystemError) Exception mask bit Defaults to 1 on warm reset

A Meaning 0 Exception not masked 1 Exception masked I

bit[7]IRQ mask bit Defaults to 1 on warm reset

I Meaning 0 Exception not masked 1 Exception masked F

bit[6]FIQ mask bit Defaults to 1 on warm reset

Link to original

F Meaning 0 Exception not masked 1 Exception masked

Registers used to configure Coretex-M Exceptions

https://interrupt.memfault.com/blog/arm-cortex-m-exceptions-and-nvic